Tutorials

Learn More

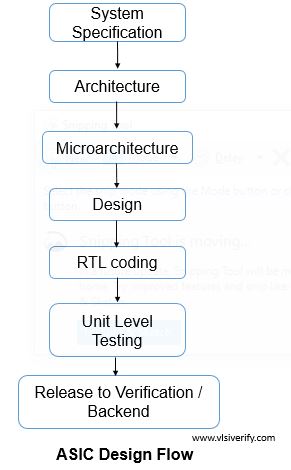

ASIC Design Flow

System Specification

At first, based on market trends and future requirements what has to be designed is being analyzed and captured as system specifications.

Architecture

As per system specifications, all features that need to be implemented in hardware and firmware/software are decided in this phase. An architectural team decides the data and control flows and can have different approaches to implement the hardware blocks and offload some work to the firmware. An optimized approach is selected considering various trade-offs like clock frequency, speed, power consumption, firmware execution time, etc.

Microarchitecture

In this phase, necessary hardware resources like design blocks, inter-block interface, and their communication protocols within the system are decided, basically it is low-level design discussions.

Design

As a part of this phase, how features will be implemented in the hardware, register configurations, and what all different design components will be used like a finite state machine (FSM), MUX, De-Mux, counters, registers, etc.

RTL Coding

The actual feature is implemented using hardware description languages (HDL) like Verilog or VHDL. It is necessary to write synthesizable code so that the synthesis tool can properly convert HDL implemented code into the actual gate-level design.

Unit Level Testing

Before releasing the design code to other teams like verification or backend, unit-level testing is performed by the designer to make sure at least the basic functionality of the design works as expected. This helps to capture and resolve basic bugs.

ASIC Flows