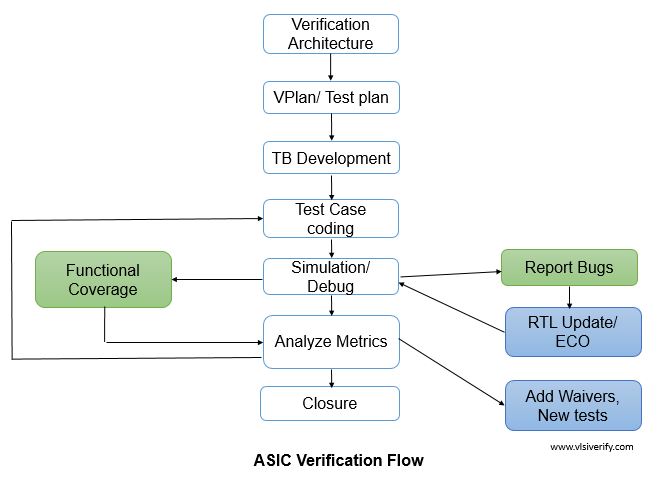

ASIC Verification Flow

The functional verification process allows verification engineers in finding bugs, checking for RTL correctness based on the design specification. The first step in the verification process is to prepare a verification plan which is tightly coupled with the design specification that involves what all features need to be tested and techniques used to verify the design under test (DUT) such as scoreboard check planning, assertions, and functional coverage writing, etc.

Verification Architecture

In the verification architectural phase, engineers decide what all verification components are required.

Verification Plan/ Testplan

The verification plan includes a test plan(list of test cases that target design features), functional coverage planning, module/block assignments to the verification engineers, checker, and assertion planning. The verification plan also involves planning for how verification components can be reused at system/ SOC level verification.

Testbench Development

As a part of testbench development, verification engineers develop testbench components, interface connections with the DUT, VIP integration with a testbench, inter-component connections within testbench (like monitor to scoreboard connection), etc.

Testcase Coding

A constraint-based random or dedicated test case is written for single or multiple features in the design. A test case also kicks off UVM-based sequences to generate required scenarios.

Simulation/ Debug

In this phase, engineers validate whether a specific feature is targetted or not, If not, again test case is modified to target the feature. With the help of a checker/ scoreboard, the error is reported if the desired design does not behave as expected. Using waveform analysis or log prints, the design or verification environment is judged and a bug is reported to the design team if it comes out to be a design issue otherwise, simulation is re-run after fixing the verification component.

Analyze Metrics

Assertions, code, and functional coverage are common metrics that are used as analysis metrics before we close the verification of the design.

IP and SOC Verification

Due to the increasing complexity of designs, functional verification is done in multiple ways like block/IP verification and System/SoC (System on Chip) verification. Let’s see how they are different from each other.

|

Block/ IP Verification |

System/ SoC Verification |

|

The focus is on verifying the functionality of individual modules/IPs. |

The focus is on verifying the integration of various design IPs in the chip. |

|

The verification involves driving all possible combinations for design testing |

The verification involves system-level scenario testing along with software configuration. |

|

All testbench components like the driver, monitor, scoreboard, agent, etc are implemented. |

Along with testbench components, co environments (C-based test/ re-using IP level components) are used. |

|

Test cases are mostly limited to dedicated module-level verification |

Sometimes, test cases are also used at ATE(Automatic Test Equipment) as part of chip bring up and a few tests for gate-level simulations (GLS) |

|

Detailed coverage is measured and analyzed |

Pin level toggle coverage is measured and analyzed. It also includes system-level interrupt functionality verification. |

|

Build/ compile time is less as compared to SoC level verification. |

Build/ compile time is much more. |

ASIC Flows