Tutorials

Learn More

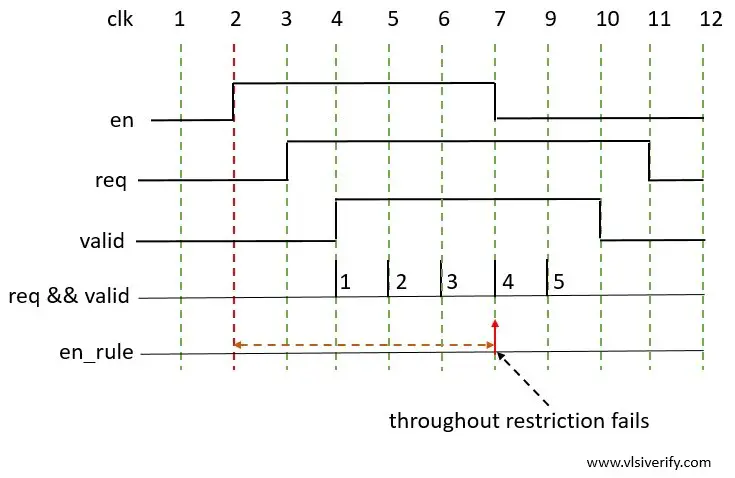

throughout Operator

The throughout operator is used under circumstances where the occurrence of certain values is prohibited while processing a transaction.

The construct exp throughout seq is an abbreviation for

exp [*0:$] intersect seq;The “exp throughout seq” matches along with finite consecutive clock ticks when seq matches along with the interval and exp also evaluates to true for each clock tick of the interval.

throughout operator Example

sequence en_rule;

@(posedge clk) $rose (en) ##0

(en) throughout (##2 (req && valid)) [*5]);

endsequence

Explanation

The signal en is low at clock tick 1 and high at clock tick 2, $rose(en) is true at clock tick 2.

To complete match of en_rule, the en signal is required to be high throughout a match of the subsequence (##1 (req && valid)) [*5]). In the above diagram, the en signal goes low before consecutive 5 clock cycles when req and valid signals are high then it is a violation of the en_rule.

SystemVerilog Assertions