Register Abstraction Layer (RAL) Model

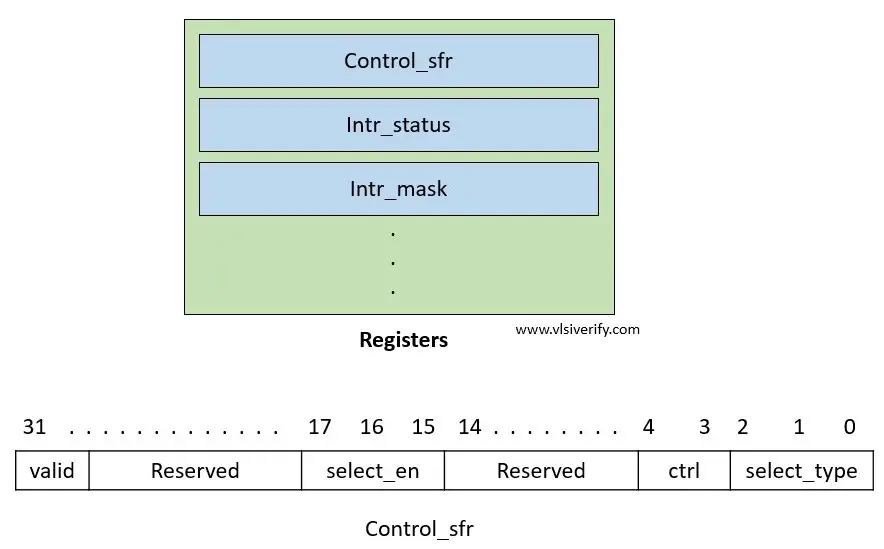

Most digital controllers or blocks have registers that can be programmed by software (commonly known as firmware). These registers are accessed by certain protocols like AXI, AHB, APB protocols, etc. Using these register software can control design behavior in a certain way. For example, design can have certain configurations which can be enabled or disabled by programming registers. Registers are commonly known as SFR (Special Function Registers).

The verification engineer is also responsible to check register accessibility and its functionality by verifying all registers with possible value, Though the UVM RAL model is not necessary for registers verification, RAL is a recommended technique that does the job efficiently.

32-bit registers are generally used in the designs.

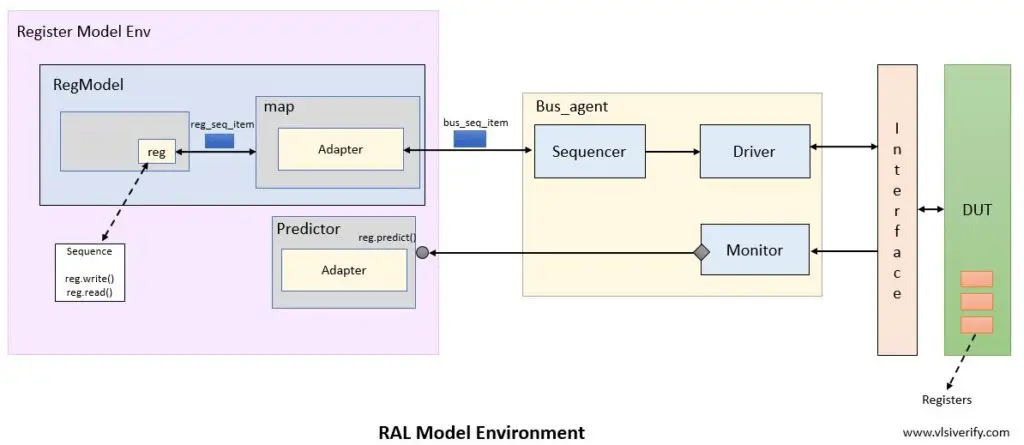

As mentioned above, software needs to do some transactions based on a supported protocol to write/ read values to/ from registers. So, for this, we need a driver, sequencer to drive sequence_item. RAL model provides a set of methods and rules that make verification engineer job easy,

The register abstraction layer provides standard base class libraries. It is used to create a memory-mapped model for registers in DUT using an object-oriented model.

The UVM RAL provides a set of classes that model DUT registers and memories. It generates stimulus to the DUT and covers some aspects of functional coverage.

“The RAL model is an abstract model for registers and memories in DUT.”

Register Model Testbench Environment

RAL provides front door access and backdoor access to the SFR.

Front door Access

A register is said to be accessed as a front door if it involves a bus interface. It does consume time in accessing the register.

Back door Access

A register is said to be accessed as a back door if it uses a simulator database to directly access the DUT register using design signals.

Advantages of the UVM RAL model

- Reusability – Same RAL model can be used in other environments for the same design. For example, block-level and system-level environments.

- Once a RAL model is integrated into the verification environment, a verification engineer can access registers by using read/write methods. Internally, actual transactions will be carried by the model.

- It defines the same set of rules so it is convenient to follow across the industry.

- Reset value can be configured as per the design requirement.

- As it uses the OOP concept, a register can be accessed with a name and methods can be called directly.

- It provides a connection to sample coverage bins.

- It has a built-in compare method that compares predicted value and actual register value.

- Internal sequencer manages to drive design signals even though parallelly multiple read/write requests have been given.

RAL Tutorials