Tutorials

Learn More

D Flip Flop with Synchronous Reset

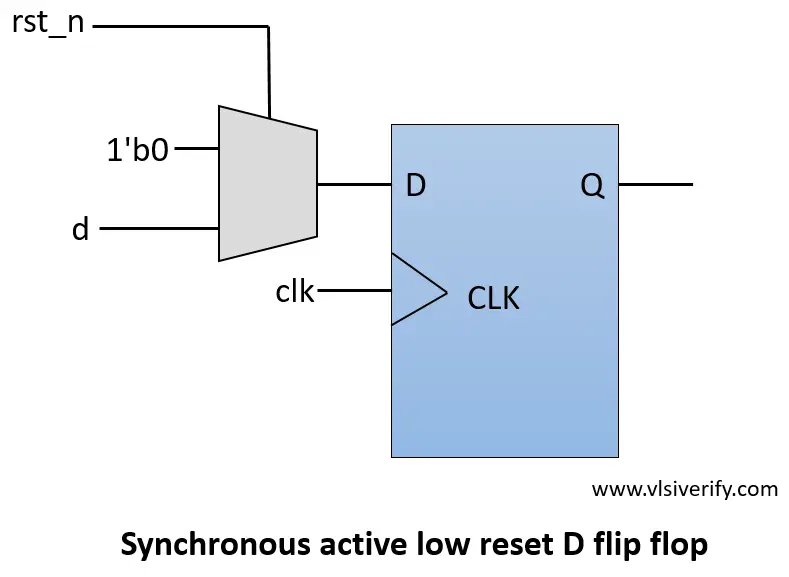

The below D flip flop is positive edge-triggered and synchronous active low reset D flip flop

As soon as reset is triggered, the output gets reset on the next posedge of a clock.

D Flip Flop with Synchronous Reset Verilog Code

module D_flipflop (

input clk, rst_n,

input d,

output reg q

);

always@(posedge clk) begin

if(!rst_n) q <= 0;

else q <= d;

end

endmoduleTestbench Code

module tb;

reg clk, rst_n;

reg d;

wire q;

D_flipflop dff(clk, rst_n, d, q);

always #2 clk = ~clk;

initial begin

clk = 0; rst_n = 0;

d = 0;

#3 rst_n = 1;

repeat(6) begin

d = $urandom_range(0, 1);

#3;

end

rst_n = 0; #3;

rst_n = 1;

repeat(6) begin

d = $urandom_range(0, 1);

#3;

end

$finish;

end

initial begin

$dumpfile("dump.vcd");

$dumpvars(1);

end

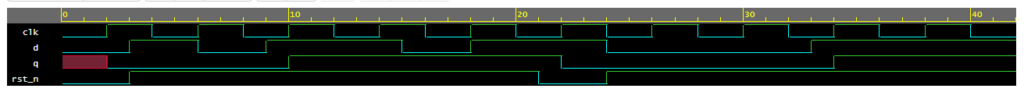

endmoduleWaveform

Verilog Codes