SystemVerilog Arrays

An array is a group of variables having the same data type. It can be accessed using an index value.

An index is a memory address and the array value is stored at that address.

Types of an array

- Fixed-size array in SystemVerilog

- Single dimensional array

- Multidimensional array

a. Two-dimensional array.

b. Three-dimensional array - Packed and Unpacked array in SystemVerilog

- Dynamic array in SystemVerilog

- Associative array in SystemVerilog

Fixed-size array in SystemVerilog

Array size is fixed throughout the simulation. Its value will be initialized with a ‘0’ value.

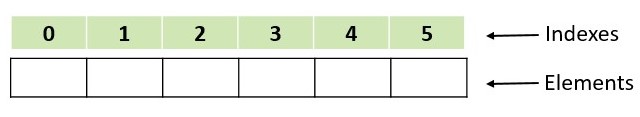

Single dimensional array

int arr [3];

int arr [2:0];

Array assignment

int arr[3] = '{5,6,7}; // Declaration, and assignment

Or

int arr[3];

arr[0] = 5;

arr[1] = 6;

arr[2] = 7;Multidimensional array

A multidimensional array is also known as an array of an array. In mathematics, we studied matrix, this can be understood as a multidimensional matrix.

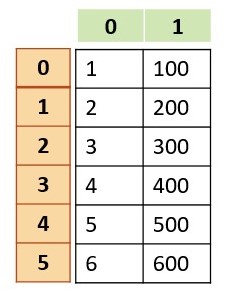

Two-dimensional array

int array[6][2] = '{'{1, 100}, '{2, 200}, '{3, 300}, '{4,400}, '{5, 500}, '{6, 600}}; // Declaration and assignment

int arr[6][2]; // Declaration

arr[0][0] = 1; // Assignment

arr[0][1] = 100;

arr[1][0] = 2;

arr[1][1] = 200;

arr[2][0] = 3;

arr[2][1] = 300;

arr[3][0] = 4;

arr[3][1] = 400;

arr[4][0] = 5;

arr[4][1] = 500;

arr[5][0] = 6;

arr[5][1] = 600;Example:

module foreach_example;

int array[6][2] = '{'{1, 100}, '{2, 200}, '{3, 300}, '{4,400}, '{5, 500}, '{6, 600}};

initial begin

foreach (array[i,j]) begin

$display("array[%0d][%0d] = %0d", i,j, array[i][j]);

end

end

endmoduleOutput:

array[0][0] = 1

array[0][1] = 100

array[1][0] = 2

array[1][1] = 200

array[2][0] = 3

array[2][1] = 300

array[3][0] = 4

array[3][1] = 400

array[4][0] = 5

array[4][1] = 500

array[5][0] = 6

array[5][1] = 600Three-dimensional array

int array[3][3][3] = '{'{'{1, 10, 100}, '{2, 20, 200}, '{3, 30, 300}},

'{'{4, 40, 400}, '{5, 50, 500}, '{6, 60, 600}},

'{'{7, 70, 700}, '{8, 80, 800}, '{9, 90, 900}}

};

Example:

module foreach_example;

int array[3][3][3] = '{'{'{1, 10, 100}, '{2, 20, 200}, '{3, 30, 300}},

'{'{4, 40, 400}, '{5, 50, 500}, '{6, 60, 600}},

'{'{7, 70, 700}, '{8, 80, 800}, '{9, 90, 900}}

};

initial begin

foreach (array[i,j, k]) begin

$display("array[%0d][%0d][%0d] = %0d", i,j, k, array[i][j][k]);

end

end

endmoduleOutput:

array[0][0][0] = 1

array[0][0][1] = 10

array[0][0][2] = 100

array[0][1][0] = 2

array[0][1][1] = 20

array[0][1][2] = 200

array[0][2][0] = 3

array[0][2][1] = 30

array[0][2][2] = 300

array[1][0][0] = 4

array[1][0][1] = 40

array[1][0][2] = 400

array[1][1][0] = 5

array[1][1][1] = 50

array[1][1][2] = 500

array[1][2][0] = 6

array[1][2][1] = 60

array[1][2][2] = 600

array[2][0][0] = 7

array[2][0][1] = 70

array[2][0][2] = 700

array[2][1][0] = 8

array[2][1][1] = 80

array[2][1][2] = 800

array[2][2][0] = 9

array[2][2][1] = 90

array[2][2][2] = 900Scalar Vs Vector

Scalar

The data object which does not have a specific range for bit/logic/reg is a scalar.

logic var1;

bit var2;

Vector

The data object which has a specific range for bit/logic/reg is a vector.

logic [5:0] var1;

bit [2:0] var2;Packed and Unpacked array

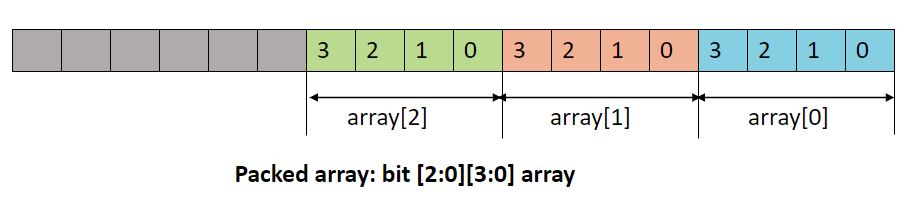

Packed array

A packed array refers to the dimension mentioned before the variable or object name. This is also known as the vector width.

Memory allocation is always a continuous set of information that is accessed by an array index.

reg [5:0] array; // [5:0] is packed dimension or vector width.

bit [2:0][3:0] array;

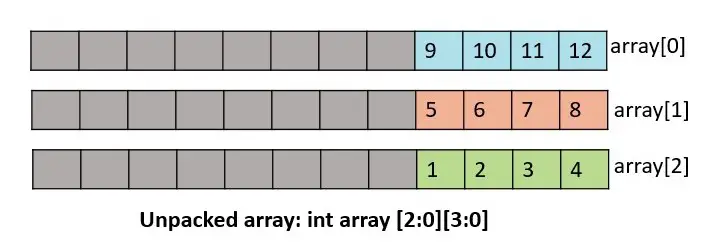

Unpacked array

An unpacked array refers to the dimension mentioned after the variable or object name.

Memory allocation may or may not be a continuous set of information.

reg arr [3:0]; // [3:0] is unpacked dimension.

int array [2:0][3:0];

Example:

module array_example;

int array [2:0][3:0] = '{'{1, 2, 3, 4},

'{5, 6, 7, 8},

'{9, 10, 11, 12}

};

initial begin

foreach (array[i,j]) begin

$display("array[%0d][%0d] = %0d", i, j, array[i][j]);

end

end

endmoduleOutput:

array[2][3] = 1

array[2][2] = 2

array[2][1] = 3

array[2][0] = 4

array[1][3] = 5

array[1][2] = 6

array[1][1] = 7

array[1][0] = 8

array[0][3] = 9

array[0][2] = 10

array[0][1] = 11

array[0][0] = 12Combination of a packed and unpacked array

All arrays mentioned above are types of static arrays.

Example:

module array_example;

bit [4:0] array[2:0][1:0] = '{'{5'h5, 5'h1},

'{5'h10, 5'h2},

'{5'h15, 5'h3}

};

initial begin

foreach (array[i,j]) begin

$display("array[%0h][%0h] = %0h", i, j, array[i][j]);

end

end

endmoduleOutput:

array[2][1] = 5

array[2][0] = 1

array[1][1] = 10

array[1][0] = 2

array[0][1] = 15

array[0][0] = 3System Verilog Tutorials