SystemVerilog Scheduling Semantics

The SystemVerilog scheduling semantics is used to describe SystemVerilog language element’s behavior and their interaction with each other. This interaction is described with respect to event execution and its scheduling.

The SystemVerilog process concurrently schedules elements such as always, always_comb, always_ff, always_latch, and initial procedural blocks, continuous assignments, asynchronous tasks, and primitives.

Processes are ultimately sensitive to event updates. The terminology of event update describes any change in a variable or net state change. For example, always @(*) is sensitive for all variables or nets used. Any change in variable or net is considered as an event update. Another example could be having multiple initial blocks in the code. The evaluation order of these initial blocks can be arbitrary depending on simulator implementation. Programming Language Interface (PLI) callbacks are used to call a user-defined external routine of a foreign language. Such PLI callbacks are also considered as an event that has to be evaluated.

Event Simulation

The SystemVerilog language works on the evaluation and execution of such events. So, it becomes important to understand how these events will be evaluated and executed. The events are scheduled in a particular order to render an event execution in a systematic way.

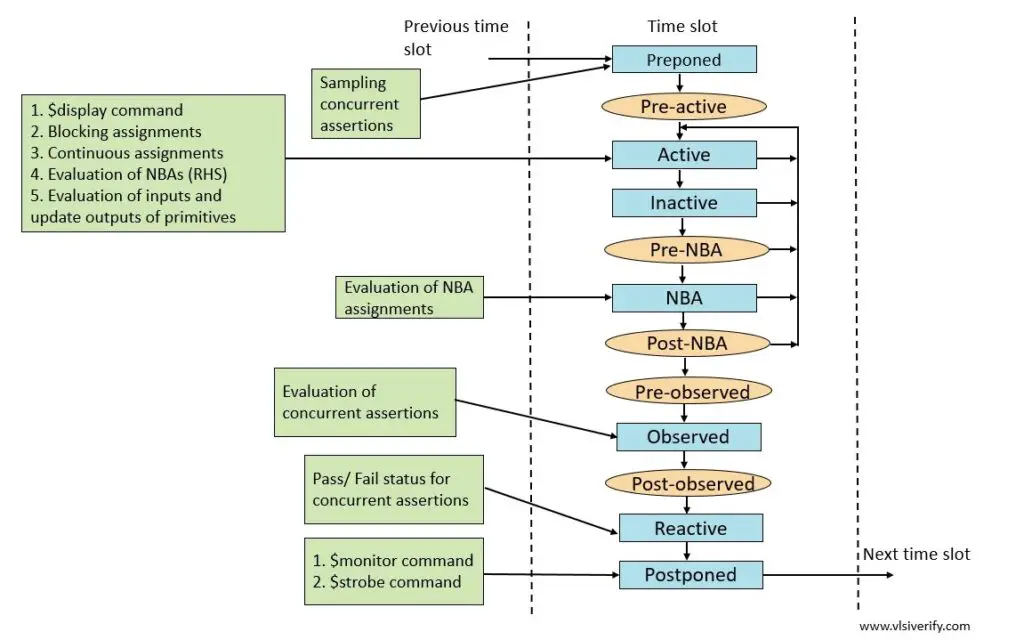

The design takes some time cycles to respond to the driven inputs to produce outputs. The simulator models the actual time for the design description that is commonly known as simulation time. A single time cycle or slot is divided into various regions and that helps out to schedule the events. The simulator executes all the events in the current time slot and then moves to the next time slot. This ensures that simulation always proceeds forward in time.

Purpose of SystemVerilog regions

- The division of time slots into ordered regions provides predictable interaction between testbench components and design.

- The property expression can be safely evaluated and the testbench can react to assertion evaluation.

SystemVerilog regions

- Preponed region

- Pre-active region

- Active region

- Inactive region

- Pre-NBA region

- NBA region

- Post-NBA region

- Observed region

- Post observed region

- Reactive region

- Postponed region

Scheduling Semantics in SystemVerilog

Preponed region

The preponed regions is executed once in each time slot that has used in sampling concurrent assertions

Pre-active region

The pre-active region is used especially for the PLI callback control point to allow user code to write and read values and create events before evaluation of events in the active region.

Active region

The active region is used to hold current events being evaluated and can be processed in any order.

Active region evaluates

- Inputs and update outputs of Verilog primitives

- Right Hand Side (RHS) of all nonblocking assignments and execute to update Left Hand Side (LHS) in the NBA region.

Active region executes

- Blocking assignments of all modules

- Continuous assignments of all modules

- $display and $finish commands.

Inactive region

The inactive region holds events to be evaluated after processing all the active events. An explicit #0 delay is scheduled in the inactive region of the current time slot.

Pre-NBA region

The pre-NBA region is used especially for the PLI callback control points to allow user code to write and read values and create events before evaluation of events in the NBA region.

NBA region

The NBA region is mainly used to update LHS of all nonblocking assignments whose RHS were evaluated in the active region.

Post-NBA region

The pre-active region is used especially for the PLI callback control point to allow user code to write and read values and create events after evaluation of events in the NBA region.

Observed region

The observed region is used to evaluate concurrent assertion which was sampled in the preponed region. The property expression evaluation must occur only once in a time slot and its pass/fail code will be scheduled in the reactive region of the same time slot. For the clocking block construct in SystemVerilog, if input skew is an explicit #0, then the value sampled in the observed region corresponds to that signal value.

Post observed region

The post observed is specially used for PLI callback control points that allow user code to read values after evaluation of properties in the observed or earlier region.

Reactive region

The reactive region is used to schedule code specified in the program block and property expression pass/fail code. The reactive region

- Executes continuous assignments in program block

- Executes blocking assignments in program block

- Execute $exit command

- Execute property expression pass/fail code.

Thus, The reactive region is an important region to schedule events for the program block.

Postponed region

The postponed region is used for the PLI callback control point that allows user code to be suspended until all active, inactive, and NBA regions have completed. It is illegal to write values to any variable or net. An event scheduling for the previous region in the current time slot is also illegal.

The $monitor and $strobe command execution happens in the postpone region. Similarly, it is also used to collect for functional coverage.

For clocking block construct in SystemVerilog, if input skew is not an explicit #0, then the value sampled in the postponed region corresponds to that signal value.

Highlights of Operations

Highlights of operation of different SystemVerilog constructs, elements, or events are as

Concurrent assertion

The concurrent assertion is sampled at a preponed region. It is evaluated at the observed region and the pass/fail code is scheduled in the reactive region.

Non-blocking assignments

The RHS of all non-blocking assignments are evaluated at the active region and executed to update LHS in the NBA region.

$monitor and $strobe

$monitor and $strobe command execution happen in the postpone region.

Clocking block constructs

If input skew is an explicit #0, then the value sampled in the observed region corresponds to that signal value else it is sampled in the postponed region.

PLI callback

In the pre-active region, the PLI callback control point allows user code to write or read values and create events before evaluation of events in the active region. Subsequently, the pre-NBA region does the same before evaluation of events in the NBA region. And the post-NBA region does the same after evaluation of events in the NBA region. In the post-observed region, PLI callback control points allow user code to read values after evaluation of properties in the observed or earlier region. Finally, the postponed region is used for the PLI callback control point that allows user code to be suspended until all active, inactive, and NBA regions have completed. It is illegal to write values to any variable or net. An event scheduling for the previous region in the current time slot is also illegal.

Program block

The initial blocks within program blocks are scheduled in the reactive region whereas initial blocks within module blocks are scheduled in the active region. This avoids race around conditions between design and testbench code.

System Verilog Tutorials