Tutorials

Learn More

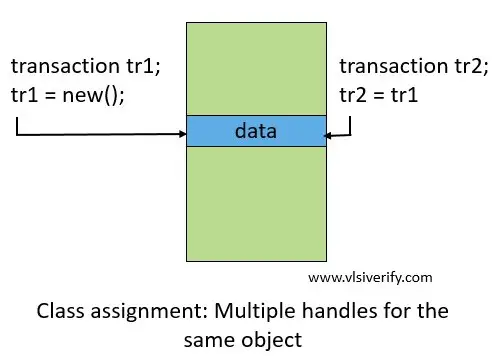

Class Assignment in SystemVerilog

Multiple handles for the same object example

In the below example, memory is created for object tr1. Class handle tr2 can also point to the same object using a simple assignment operator. After the assignment, anyone tr1 or tr2 handle can change the ‘data’ value.

class transaction;

bit [31:0] data;

endclass

module class_example;

transaction tr1, tr2;

initial begin

tr1 = new();

tr1.data = 5;

tr2 = tr1;

$display("tr1.data = %0h", tr1.data);

$display("tr2.data = %0h", tr2.data);

tr2.data = 10;

$display("tr1.data = %0h", tr1.data);

$display("tr2.data = %0h", tr2.data);

end

endmoduleOutput:

tr1.data = 5

tr2.data = 5

tr1.data = a

tr2.data = aRefer SystemVerilog Polymorphism to understand child class handle assignment to the base class and vice-versa.

System Verilog Tutorials