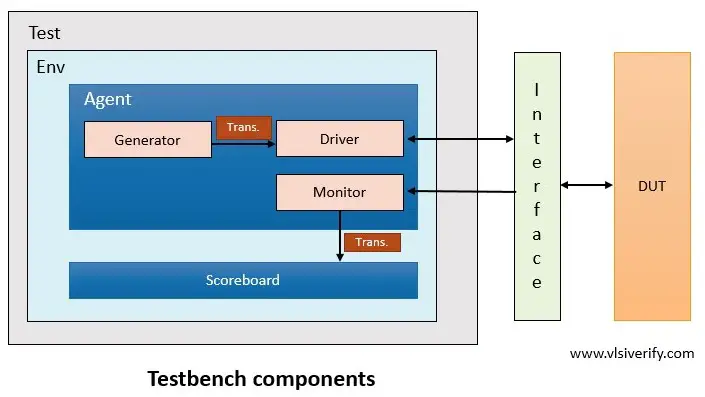

Verification process and Testbench

To check the functional correctness of the design, testbench is written. The verification process allows verification engineers in finding bugs, checking for RTL correctness based on the design specification. The first step in the verification process is to prepare a verification plan which is tightly coupled with the design specification that involves what all features need to be tested and techniques used to verify the design under test (DUT) such as scoreboard check planning, assertions, and functional coverage writing, etc. The testbench is a setup or environment that allows verification of DUT.

The testbench is responsible for

- Generating input stimulus

- Driving an input stimulus

- Monitor design activity at the output and input level.

- Compare output transaction correctness based on the driven input stimulus.

- Sampling function converges and assertion correctness.

Testbench components

- Transaction

- Generator

- Driver

- Monitor

- Agent

- Scoreboard

- Environment

- Testbench top

- Test

Transaction

The transaction is a packet that is driven to the DUT or monitored by the monitor as a pin-level activity.

In simple terms, the transaction is a class that holds a structure that is used to communicate with DUT.

Generator

The generator creates or generates randomized transactions or stimuli and passes them to the driver.

Driver

The driver interacts with DUT. It receives randomized transactions from the generator and drives them to the driven as a pin level activity.

Monitor

The monitor observes pin-level activity on the connected interface at the input and output of the design. This pin-level activity is converted into a transaction packet and sent to the scoreboard for checking purposes.

Agent

An agent is a container that holds the generator, driver, and monitor. This is helpful to have a structured hierarchy based on the protocol or interface requirement.

Scoreboard

The scoreboard receives the transaction packet from the monitor and compares it with the reference model. The reference module is written based on design specification understanding and design behavior.

Environment

An environment allows a well-mannered hierarchy and container for agents, scoreboards.

Testbench top

The testbench top is a top-level component that includes interface and DUT instances. It connects design with the testbench.

Test

The test is at the top of the hierarchy that initiates the environment component construction and connection between them. It is also responsible for the testbench configuration and stimulus generation process.

System Verilog Tutorials